Sharp CE-158 Manual do Utilizador Página 16

- Página / 36

- Índice

- MARCADORES

Avaliado. / 5. Com base em avaliações de clientes

All and more about Sharp PC-1500

at

http:f/www.PC-1500.info

5 PERIPHERAL STATUS

IN

TERRUPT (PSI):

This

bit

is

se t high by a

high·t<>-lo

w voltage transition

of

Term

.

37

(PSI

).

The INTERRUPT

out

.

put

(Term. 13) is also asserted ( INT = low)

whe

n this bit

is

set.

6

TRANSMITTER SHI

FT

REGI

ST

ER E

MPTY

(TSRE):

Wh

en set high, this bit indicates that the Transmitter Shift Register has completed ser

ia

l trans·

mission

of a

fu

ll

character including st

op

bit(s).

It

remains sci until the start or trans

mi

ssion o f

rh

e next cha

ra

cter.

7 TRANSMITT

ER

HOLDING R

EG

ISTER EMPTY (THRE):

Wh

en set high, this bi t indicates that the Transmitt

er

Hol ding Register has transferred its

contents to

the

Transmitter

Sh

ift Register and may be reloaded

wi

th a new character. Setting this

bit

also sets t

he

THRE

output

(Term. 22) low

and

causes an INTERRUPT (I

NT=

low),

if

TR is

high.

4. Peripheral Interface

14

In addition

to

serial data in and o ut, fo

ur

signals arc provided for communication with a peripheral.

n ie REQUEST TO SET

NT

(RTS) o

utput

sign

al al

er

ts

th

e periphe

ra

l to

ge

l ready 10 recei

ve

da

ta

.

The

CLEAR TO SE

ND

(CTS)

inpu

t sign

al

is

the response, signalling that the peripheral is ready. The

EXTERNAL STATUS (ES) input latches a peripheral Slatus level, and

the

PERIPHERAL STATUS

IN

TER

RUPT

(P

SI) input

senSC$

a status edge (high·lo·low)

and

also generates an interrupt. Fo r

example, the modern DATA

CA

RR

IE

R DETECT line could be connected

to

the

l'sfinpu

l

on

t

he

U

ART

in ord

er

to

si

gn

al

t

he

microprocessor

th

at t

ra

nsmission failed because of loss

of

the

carri

er

on the commu

ni

cations lin

e.

The PSI and ES bits arc stored in the Sta tus Regist

er

(See Fi

g.

4 ).

~

:-

1oc•

so1

-----i

: S

fAAT

Bil

PAHnY

I

srOP

e

rr

t

A(AO••

~~--

-t-

-----~------------

-T-'--

-

--t

I

TT~

TPS

___

__,

OE

•

'------

--------

-

---

_.)

;

!--

• C

OL

:

ICP~

:----:

···

~-

---------------------

-.;,....;_

1'C

Pt

,.....-.

Ft;I

- -

-------

---

-----

-

--

-=-

-'--

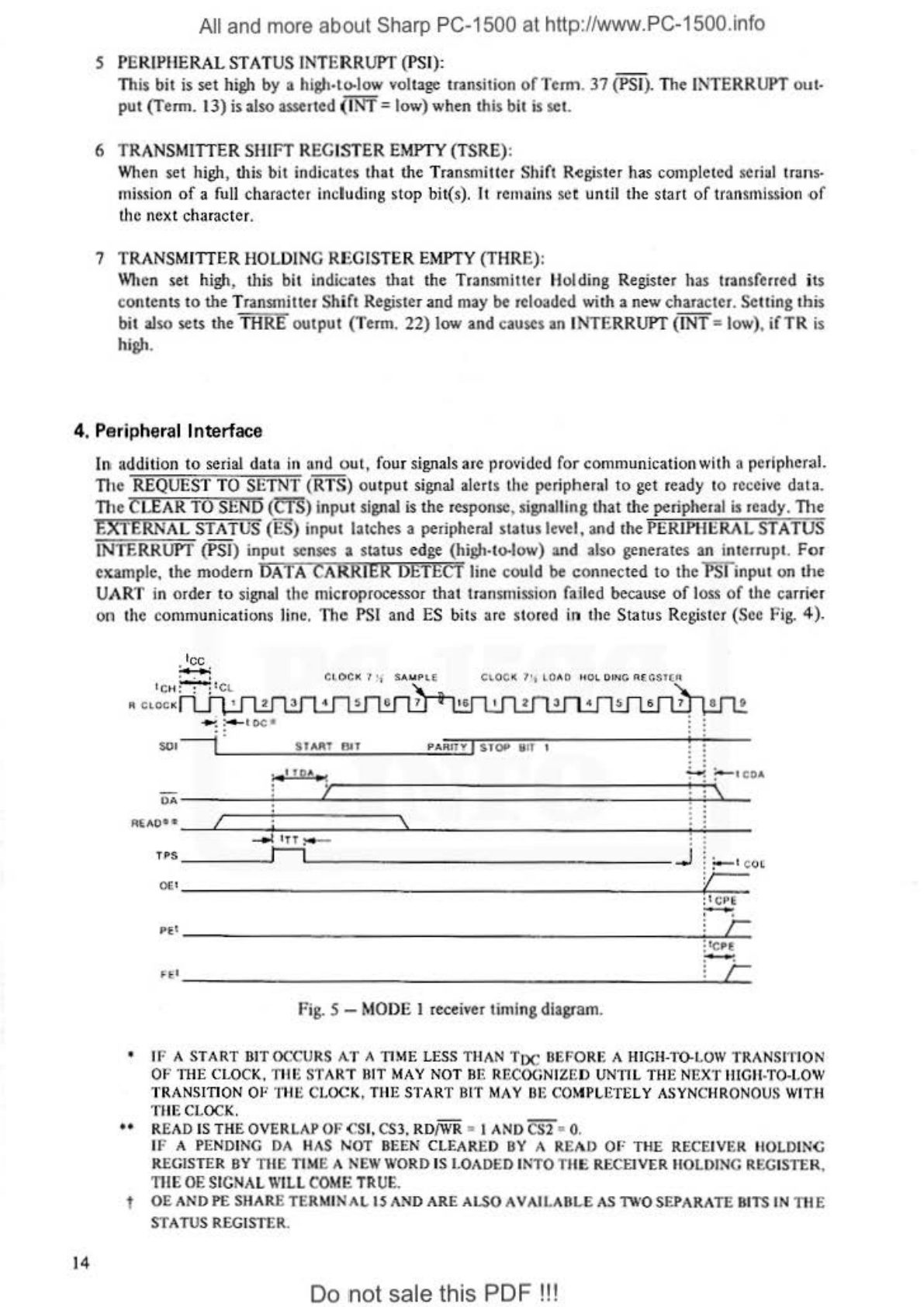

Fig. 5 - MODE I receiver timing diagram.

' I

I'

A

ST

A

RT

BIT

OC

CU

RS AT A

TIME

LESS

THA

N

Toe

DEFO

RE

A f

ll

GH·

'f().LOW TRANSI

TIO

N

OF

'Jl

l E

CLO

CK. THE

ST

ART

BIT

MAY

NO

T RE RECOG

NIZE

D UN

TI

L THE NE

XT

J

llG

ll

·T

O·l .. OW

TRANSITION

OF

THE

CLOC

K, THE

ST

AR

T

arr

MAY

IHO

COM

PLE

TELY

ASYNC

HR

ONOUS WI

T.H

TllEC

L

OC

K.

"

READ JS

TH

E

OVER

LAP

OF

CSI,

CS

3.

R D/WR • 1 A

ND

CS2

•

O.

II'

A PE

ND

I

NG

DA

HAS

N

OT

B

EEN

CL

EARE D BY A REA D O F

THE

R

ECE

IVER

HOLDING

R

EGIS

TER BY

THE

TIME A NEW

WO

R D IS

LOADED

t

NTO

Tll

E

RECEIVE

R

llOLDINC

REG

I

STE

R,

Til

£

0F.

SIGNAL WILL

COME

TRUE.

t

0£

AND

P£

SHARE

TER

M

INAL

JS

AN

D

ARE

ALSO

AVAILABLE

AS

1'1'0

SEPARATE

BITS JN

TIIE

STATUS

REG

I

STER

.

Do

not sale this PDF !!!

- SERVICE 1

- 7, S bit 3

- "" 4

- BLOCK DIAGRAM 5

- Circuit 6

- I : Data 7

- Do not sale this PDF !!! 7

- AEGULATOA 8

- • G1 • 9

- INTERRUl'T 10

- LSI Discription 11

- 00 125 100 125 12

- 00 125 12

- ' 13

- PDF !!! 14

- = I) and 15

- II' 16

- 5 - JOO 17

- Do not sale this PDF !!! 18

- 10 the 19

- 7. IC PIN CONNECTION 20

- <> 21

- "' 22

- . " '• 25

- ~;:;=::::rr-~ 26

- PARTS GUIDE 27

- > Cl 29

- <' 30

- XBBSD26P 31

- '-" 32

- NI< 33

- CORPORATION 36

(89 páginas)

(89 páginas)

(210 páginas)

(210 páginas) (11 páginas)

(11 páginas) (14 páginas)

(14 páginas) (15 páginas)

(15 páginas)

(28 páginas)

(28 páginas)

Comentários a estes Manuais